����Ӣ������Ӌ(j��)��C(j��)�M��ԭ���������棩���ƌW(xu��)���������

�n���v��

ǰ��

��1�¡�Ӌ(j��)��C(j��)ϵ�y(t��ng)��Փ

1.1��Ӌ(j��)��C(j��)��͑�(y��ng)��

1.2��Ӌ(j��)��C(j��)ϵ�y(t��ng)�M��

1.2��Ӌ(j��)��C(j��)ϵ�y(t��ng)�M�ɣ��m(x��)��

1.3��Ӌ(j��)��C(j��)�İl(f��)չ

1.4��Ӌ(j��)��C(j��)ϵ�y(t��ng)�ČӴνY(ji��)��(g��u)

�����Y(ji��)

��2�¡��\(y��n)�㷽�����\(y��n)����

2.1����(sh��)��(j��)�c���ֵı�ʾ����

2.1����(sh��)��(j��)�c���ֵı�ʾ�������m(x��)1��

2.1����(sh��)��(j��)�c���ֵı�ʾ�������m(x��)2��

2.1����(sh��)��(j��)�c���ֵı�ʾ�������m(x��)3��

2.2�����c(di��n)�ӷ����p���\(y��n)��

2.2�����c(di��n)�ӷ����p���\(y��n)�㣨�m(x��)��

2.3�����c(di��n)�˷��\(y��n)��

2.3�����c(di��n)�˷��\(y��n)�㣨�m(x��)��

2.4�����c(di��n)�����\(y��n)��

2.5�����c(di��n)�\(y��n)�����ĽM��

2.5�����c(di��n)�\(y��n)�����ĽM�ɣ��m(x��)��

2.6�����c(di��n)�\(y��n)�㷽�����c(di��n)�\(y��n)����

2.6�����c(di��n)�\(y��n)�㷽�����c(di��n)�\(y��n)�������m(x��)��

�����Y(ji��)

��3�¡��惦(ch��)ϵ�y(t��ng)

3.1���惦(ch��)������

3.2���S�C(j��)�x���惦(ch��)��

3.2���S�C(j��)�x���惦(ch��)�����m(x��)1��

3.2���S�C(j��)�x���惦(ch��)�����m(x��)2��

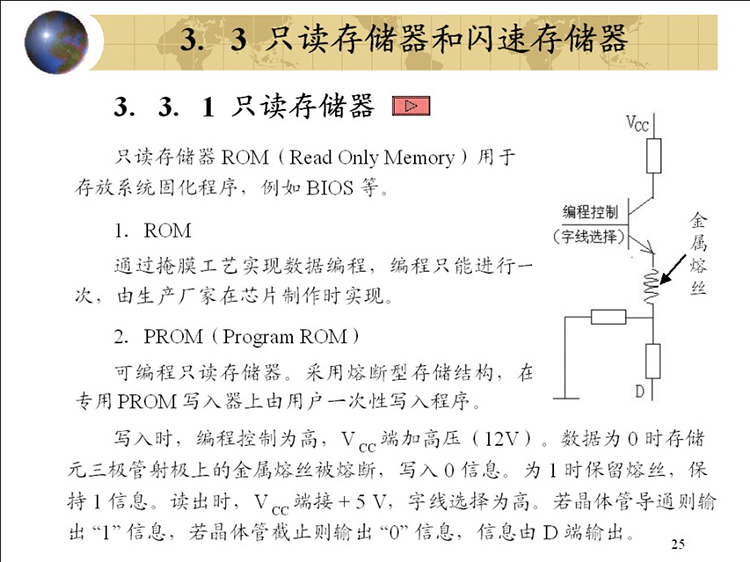

3.3��ֻ�x�惦(ch��)�����W�ٴ惦(ch��)��

3.4�����ٴ惦(ch��)��

3.4�����ٴ惦(ch��)�����m(x��)��

3.5��Cache�惦(ch��)��

3.5��Cache�惦(ch��)�����m(x��)��

3.6��̓�M�惦(ch��)��

3.7���惦(ch��)���o(h��)

�����Y(ji��)

��4�¡�ָ��ϵ�y(t��ng)

4.1��ָ��ϵ�y(t��ng)�İl(f��)չ������Ҫ��

4.2��ָ���ʽ

4.2��ָ���ʽ���m(x��)��

4.3��ָ��͔�(sh��)��(j��)�Č�ַ��ʽ

4.3��ָ��͔�(sh��)��(j��)�Č�ַ��ʽ���m(x��)1��

4.3��ָ��͔�(sh��)��(j��)�Č�ַ��ʽ���m(x��)2��

4.4���ї���ַ��ʽ

4.5������ָ��

�����Y(ji��)

��5�¡�����̎����

5.1��CPU�Ĺ��ܺͽM��)

5.2��ָ������

5.2��ָ�����ڣ��m(x��)��

5.3���r(sh��)��a(ch��n)�����Ϳ��Ʒ�ʽ

5.4�����������

5.5�������O(sh��)Ӌ(j��)���g(sh��)

5.6��Ӳ����������

5.7�����y(t��ng)CPU

5.7�����y(t��ng)CPU���m(x��)��

5.8����ˮCPU

5.9��RISC��CPU

5.10����ý�wCPU

�����Y(ji��)

��6�¡�ϵ�y(t��ng)����

6.1�������ĸ���ͽY(ji��)��(g��u)�ΑB(t��i)

6.1�������ĸ���ͽY(ji��)��(g��u)�ΑB(t��i)���m(x��)��

6.2�������ӿ�

6.3�������ٲá����r(sh��)�͔�(sh��)��(j��)����ģʽ

6.3�������ٲá����r(sh��)�͔�(sh��)��(j��)����ģʽ���m(x��)��

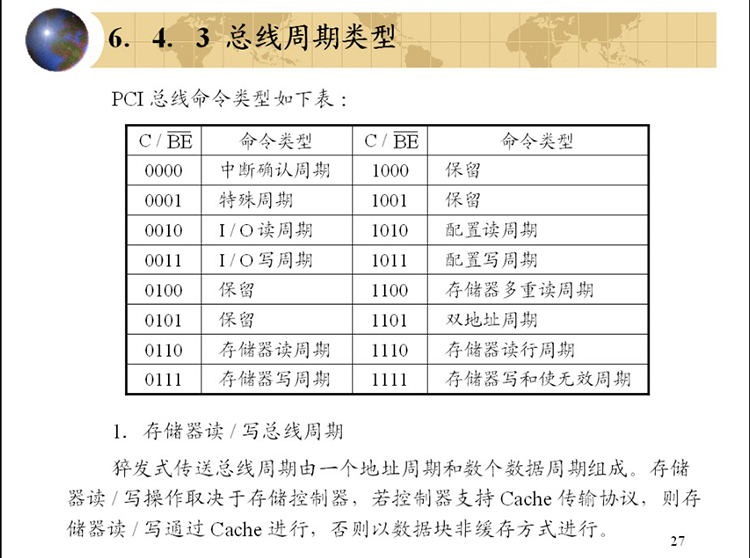

6.4��PCI����

6.4��PCI�������m(x��)��

6.5��ISA������Futurebus+����

�����Y(ji��)

��7�¡�����O(sh��)��

7.1������O(sh��)�����

7.2���@ʾ�O(sh��)��

7.2���@ʾ�O(sh��)�䣨�m(x��)1��

7.2���@ʾ�O(sh��)�䣨�m(x��)2��

7.3��ݔ���O(sh��)��

7.4����ӡ�O(sh��)��

7.5���ű���惦(ch��)��

7.5���ű���惦(ch��)�����m(x��)1��

7.5���ű���惦(ch��)�����m(x��)2��

7.6����P�惦(ch��)�O(sh��)��

�����Y(ji��)

��8�¡�ݔ��ݔ��ϵ�y(t��ng)

8.1�����O(sh��)���r(sh��)��ʽ�c��Ϣ���Q��ʽ

8.2�������ԃ��ʽ

8.3�������Дʽ

8.3�������Дʽ���m(x��)1��

8.3�������Дʽ���m(x��)2��

8.4��DMA��ʽ

8.4��DMA��ʽ���m(x��)��

8.5��ͨ����ʽ

�n�̿���(f��)��(x��)

�n�̿���(f��)��(x��)

�n�̿���(f��)��(x��)(�m(x��)1)

�n�̿���(f��)��(x��)(�m(x��)2).

.................

ҕ�l�؈D��

![����h��W(xu��)��[���]Ӌ(j��)��C(j��)�M��ԭ��ҕ�l�̳�(48�v)-���}��0 ����h��W(xu��)��[���]Ӌ(j��)��C(j��)�M��ԭ��ҕ�l�̳�(48�v)-���}��0](http://www.bmm520.net/down368/allimg/140405/1_040512394A4T.jpg)